# Diploma Thesis

Evaluation of publicly available Barrier–Algorithms and Improvement of the Barrier–Operation for large–scale Cluster–Systems with special Attention on InfiniBand<sup>TM</sup>Networks

Torsten Höfler

htor@informatik.tu-chemnitz.de

Advisers: Dipl.-Inf. T. Mehlan, Dipl.-Inf. F. Mietke

Supervisor: Prof. Dr.-Ing. W. Rehm

# Task of the Thesis

The diploma thesis intends to improve the well–known barrier–operation. This operation is offered by almost every message–passing–system. A wide range of parallel applications depend on the efficiency of the barrier–algorithm. The possibility of providing a barrier of constant time complexity has to be investigated. An optimal barrier–algorithm would need constant time, no matter how much computing nodes are invoked. This research results in suggestions how to provide a well performing implementation of the barrier.

To determine the usability of advanced network services, the performance of special facilities of InfiniBand has to be measured. The main focus lies on the InfiniBand multicast service, the InfiniBand atomic operations and the InfiniBand RDMA capabilities. This evaluation provides basic knowledge to decide which network facilities are suitable to implement barrier–algorithms. Moreover the InfiniBand specification is searched for other facilities supporting barrier–algorithms efficiently.

It is also considered to use hardware support to improve the barrier–operation. Different approaches for an acceleration of the barrier–operation have to be discussed. It shall be determined whether network switches can be modified to improve the barrier. Especially extensions to InfiniBand switches shall be discussed. Furthermore some alternatives shall be considered. Thus an investigation of dedicated barrier– and broadcast–networks and bus–based networks shall be performed.

The diploma thesis has to result in a statement explaining the mechanisms and algorithms that are best suitable to implement the barrier–operation. The main goal is to achieve a barrier with constant time complexity for large numbers of computing nodes. To preserve this behavior some assumptions have to be made. This applies to the processing speed of network devices and computing nodes as well as to the network topology. The assumptions and prerequisites necessary to achieve constant time for barriers have to be explained.

# **Primary Theses**

- 1. It is possible to create a constant barrier–operation for large–scale cluster systems.

- 2. The preceding work does not take into account the theoretical foundations properly.

## Thesis Declaration

I hereby declare that this diploma thesis was composed by myself and all work included has been done by me.

Chemnitz, 29th March 2005

Torsten Höfler

# Abstract

The MPI\_Barrier-collective operation, as a part of the MPI-1.1 standard, is extremely important for all parallel applications using it. The latency of this operation increases the application run time and can not be overlaid. Thus, the whole MPI performance can be decreased by unsatisfactory barrier latency. The main goals of this work are to lower the barrier latency for InfiniBand<sup>TM</sup> networks by analyzing well known barrier algorithms with regards to their suitability within InfiniBand<sup>TM</sup> networks, to enhance the barrier operation by utilizing standard InfiniBand<sup>TM</sup> operations as much as possible, and to design a constant time barrier for InfiniBand<sup>TM</sup> with special hardware support. This partition into three main steps is retained throughout the whole thesis. The first part evaluates publicly known models and proposes a new more accurate model (LoP) for InfiniBand<sup>TM</sup>. All barrier algorithms are evaluated within the well known LogP and this new model. Two new algorithms which promise a better performance have been developed. A constant time barrier integrated into  $InfiniBand^{TM}$  as well as a cheap separate barrier network is proposed in the hardware section. All results have been implemented inside the Open MPI framework. This work led to three new Open MPI collective modules. The first one implements different barrier algorithms which are dynamically benchmarked and selected during the startup phase to maximize the performance. The second one offers a special barrier implementation for  $InfiniBand^{TM}$  with RDMA and performs up to 40% better than the best solution that has been published so far. The third implementation offers a constant time barrier in a separate network, leveraging commodity components, with a latency of only 2.5 µs. All components have their specialty and can be used to enhance the barrier performance significantly.

# Contents

| 1        | Intr     | roduction                                                                                                                                                            |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1      | Organization/Structure of the Document                                                                                                                               |

|          | 1.2      | MPI Standard                                                                                                                                                         |

|          |          | 1.2.1 The MPL_Barrier() Call                                                                                                                                         |

|          |          | 1.2.2 Available MPI Implementations                                                                                                                                  |

|          | 1.3      | InfiniBand <sup>TM</sup> $\dots$                                                             |

|          |          | 1.3.1 InfiniBand <sup>TM</sup> Architecture $\ldots$                                                                                                                 |

|          |          | 1.3.2 Hardware Queuing                                                                                                                                               |

|          |          | 1.3.3 Connection Management                                                                                                                                          |

|          |          | 1.3.4 Options for Message Passing                                                                                                                                    |

|          |          | 1.3.5 Interacting with the HCA                                                                                                                                       |

|          | 1.4      | Open MPI                                                                                                                                                             |

|          |          | 1.4.1 Component Framework                                                                                                                                            |

|          |          | 1.4.2 A Components Lifecycle                                                                                                                                         |

|          | 1.5      | Summary                                                                                                                                                              |

|          |          |                                                                                                                                                                      |

| <b>2</b> | Soft     | tware Solution 1                                                                                                                                                     |

|          | 2.1      | Models for Parallel Computation                                                                                                                                      |

|          |          | 2.1.1 Introduction                                                                                                                                                   |

|          |          | 2.1.2 Related Work                                                                                                                                                   |

|          |          | 2.1.3 Organization                                                                                                                                                   |

|          |          | 2.1.4 Characterization of available Models                                                                                                                           |

|          | 2.2      | Barrier Algorithms                                                                                                                                                   |

|          |          | 2.2.1 Algorithms Performing Phase 3                                                                                                                                  |

|          |          | 2.2.2 Algorithms Omitting Phase 3                                                                                                                                    |

|          |          | 2.2.3 Summary of Algorithms                                                                                                                                          |

|          |          | 2.2.4 Proof of Optimality                                                                                                                                            |

|          |          | 2.2.5 Evaluating the LogP Predictions for TCP/IP                                                                                                                     |

|          |          | 2.2.6 Two new Algorithms for Barrier Synchronization                                                                                                                 |

|          | 2.3      | Proposal of a Model for InfiniBand <sup>TM</sup> $\dots \dots \dots$ |

|          |          | 2.3.1 Message Passing Options 44                                                                                                                                     |

|          |          | 2.3.2 The HCA Processor                                                                                                                                              |

|          |          | 2.3.3 Hardware Parallelism                                                                                                                                           |

|          |          | 2.3.4 Measuring the Parameters                                                                                                                                       |

|          |          | 2.3.5 A Benchmark of the LoP Model                                                                                                                                   |

|          |          | 2.3.6 Benchmark Results                                                                                                                                              |

|          | <u> </u> | 2.3.7 Choosing the Optimal Solution to the Problem                                                                                                                   |

|          | 2.4      | Summary                                                                                                                                                              |

| 3        | Har      | rdware Solution 62                                                                                                                                                   |

| J        | 3.1      | Barrier Support in the Data Network                                                                                                                                  |

|          | 0.1      | 3.1.1 Single Switch                                                                                                                                                  |

|          | 3.2      | Barrier Support in a dedicated Network                                                                                                                               |

|          | 0.4      | 3.2.1 Proof of Concept Design                                                                                                                                        |

|          |          | 3.2.1       From of Concept Design       6         3.2.2       Runtime and Scalability       6                                                                       |

|          |          | 5.2.2 Runting and Scalability $\ldots \ldots 0$                                                |

|              |                                     | 3.2.3 Further Ideas                               |  |  |  |  |  |  |

|--------------|-------------------------------------|---------------------------------------------------|--|--|--|--|--|--|

|              | 3.3                                 | Summary 6                                         |  |  |  |  |  |  |

| 4            | Practical Results and Conclusion 69 |                                                   |  |  |  |  |  |  |

|              | 4.1                                 | Implementation                                    |  |  |  |  |  |  |

|              |                                     | 4.1.1 Software Barrier                            |  |  |  |  |  |  |

|              |                                     | 4.1.2 Hardware Barrier                            |  |  |  |  |  |  |

|              |                                     | 4.1.3 InfiniBand <sup>TM</sup> Barrier $\ldots$ 7 |  |  |  |  |  |  |

|              | 4.2                                 | Benchmark Environment                             |  |  |  |  |  |  |

|              |                                     | 4.2.1 Mozart                                      |  |  |  |  |  |  |

|              |                                     | 4.2.2 CLiC                                        |  |  |  |  |  |  |

|              |                                     | 4.2.3 Oscar                                       |  |  |  |  |  |  |

|              | 4.3                                 | Benchmark Applications                            |  |  |  |  |  |  |

|              |                                     | 4.3.1 Expected Results                            |  |  |  |  |  |  |

|              |                                     | 4.3.2 The Microbenchmark                          |  |  |  |  |  |  |

|              |                                     | 4.3.3 The Application Abinit                      |  |  |  |  |  |  |

|              | 4.4                                 | Microbenchmark Results                            |  |  |  |  |  |  |

|              |                                     | 4.4.1 Software Barrier                            |  |  |  |  |  |  |

|              |                                     | 4.4.2 Hardware Barrier                            |  |  |  |  |  |  |

|              |                                     | 4.4.3 InfiniBand <sup>TM</sup> Barrier $\ldots$ 7 |  |  |  |  |  |  |

|              | 4.5                                 | Application Results                               |  |  |  |  |  |  |

|              | 4.6                                 | Conclusion and Future Work                        |  |  |  |  |  |  |

|              | 4.7                                 | Acknowledgments                                   |  |  |  |  |  |  |

| $\mathbf{A}$ | Appendix 7                          |                                                   |  |  |  |  |  |  |

|              |                                     | List of Links                                     |  |  |  |  |  |  |

|              |                                     | List of Figures                                   |  |  |  |  |  |  |

|              |                                     | List of Listings                                  |  |  |  |  |  |  |

|              |                                     | List of Pseudocode-Listings                       |  |  |  |  |  |  |

|              |                                     | List of Tables                                    |  |  |  |  |  |  |

|              | A.6                                 | Glossary                                          |  |  |  |  |  |  |

|              | -                                   | References                                        |  |  |  |  |  |  |

|              |                                     | Theses                                            |  |  |  |  |  |  |

# Chapter 1

# Introduction

In general, a barrier operation is used to synchronize a number of processes. Thus, it can be seen as a synchronization primitive for parallel systems and can be useful to divide the application into different loosely coordinated phases. For example, a given application could differ between communication and computation steps, synchronized by a barrier operation. This prevents data from being sent before it is valid and overwriting of buffers during the calculation. The semantics for this operation define that each process calls the barrier function and the function does not return until all processes did so. This function is part of the MPI collective framework and therewith regarding to Amdahls Law [Amd00] very time critical. The time to complete a barrier has to be reduced as far as possible. This paper is mainly based on the barrier syntax and semantics defined in the MPI standard (see section 1.2). However, this does not limit the use of the achieved results to only this application domain. The concepts and algorithms which will be developed can be generalized for each synchronization problem in a parallel system. A big part of this paper is bound tightly to InfiniBand<sup>TM</sup> however parts of the developed methodologies can also be generalized for usage with any other interconnect network.

## 1.1 Organization/Structure of the Document

The first part of this thesis introduces several basic terms and assumptions which are used throughout the following chapters. The fundamental software to benchmark the results is described in terms of suitability and implementation details in part two of this introduction. Chapter 2 describes different models for parallel computation and their eligibility for modelling the barrier operation for InfiniBand<sup>TM</sup>. Different published barrier algorithms are analyzed in the context of the chosen model and the correctness of the predictions is validated with benchmarks. Two new barrier algorithms which are able to exploit hardware parallelism are proposed and evaluated in the second part of chapter 2. In addition, a new model will be developed and parametrized with benchmark results at the end of this chapter to satisfy the special needs of the barrier modelImg for InfiniBand<sup>TM</sup> networks. A new hardware solution to incorporate barrier support into InfiniBand<sup>TM</sup> switches or a separate barrier network is proposed in chapter 3 followed by the practical evaluation of all developed barrier techniques presented in this thesis.

## 1.2 MPI Standard

MPI stands for Message Passing Interface, which focuses on providing a widely used standard for writing parallel programs. The main target is to unify the conflicting requirements ease-of-use, portability, efficiency and flexibility for all HPC platforms. A complete list of goals stated in the MPI Standard 1.1 [For95] is shown in the following enumeration.

- Design an application programming interface (not necessarily for compilers or a system implementation library)

- Allow efficient communication: Avoid memory-to-memory copying and allow overlap of computation and communication and offload to a communication coprocessor, where available.

- Allow implementations that can be used in a heterogeneous environment.

- Allow convenient C and Fortran 77 bindings for the interface.

- Assume a reliable communication interface: The user needs not cope with communication failures. Such failures are handled by the underlying communication subsystem.

- Define an interface that is not too different from current practice, such as PVM, NX, Express, p4, etc., and provide extensions that allow greater flexibility.

- Define an interface that can be implemented on many vendor's platforms, with no significant changes in the underlying communication and system software.

- Semantics of the interface should be language independent.

- The interface should be designed to allow thread-safety.

#### List 1.1: MPI 1.1 goals

The design process started officially in 1992 when Dongarra, Hempel, Hey, and Walker proposed a preliminary draft, known as MPI-1, to the community. This ongoing development was promoted by the newly founded MPI Forum<sup>1</sup> which finished the MPI-1 review in February 1993. This first draft was intended as a starting point and covered only point to point communication and some very basic origins for the design of collective operations. An official version of this draft was released to the public at the Supercomputing 93 conference in November 1993.

The MPI Forum continued its work with the participation of over 40 organizations and proposed a final version of the MPI-1.0 standard in May 1994. This standard was swiftly superseeded with the MPI-1.1 standard in June 1995. The standardization process of MPI-2 started in April 1995 and led to a final MPI-2 document in April 1997 as an addition to MPI-1.1. Since then, the community concentrates on implementing the proposed standards in an efficient way.

It is explicitely stated that the design focuses on improving the performance and scalability of parallel computers with specialized interconnect hardware (section 1.3 in [For95]). This thesis focuses on improving the performance of the MPI\_Barrier() operation stated in the standard by utilizing special features of the InfiniBand<sup>TM</sup> network or hardware support.

The remainder of this section describes the semantics of the barrier call described in the MPI-1.1 standard and the available Open Source libraries which can be used to test and validate the results.

## 1.2.1 The MPI\_Barrier() Call

The barrier call is standardized as a collective operation in MPI-1.1 as MPI\_Barrier(MPI\_Comm comm). The communicator comm is a logical process group wherein the operation is performed. There are several predefined communicators like MPI\_COMM\_WORLD (includes all processes inside the MPI job) and MPI\_COMM\_SELF (points to the process itself). The semantics of this call are easily described as:

"MPI\_BARRIER blocks the caller until all group members have called it. The call returns at any process only after all group members have entered the call." (chapter 4.3 in [For95])

<sup>&</sup>lt;sup>1</sup>MPI Forum [http://www.mpi-forum.org]

## 1.2.2 Available MPI Implementations

Todays most important available open source MPI implementations include MPICH<sup>2</sup> and LAM/MPI<sup>3</sup>. A new approach started by the Open HPC group to develop a new MPI implementation called Open MPI<sup>4</sup>, which is mainly a consolidation of different MPI implementations (FT-MPI<sup>5</sup>, LA-MPI<sup>6</sup>, LAM/MPI<sup>7</sup> and PACX-MPI<sup>8</sup>), has the potential to become an important library in the near future.

The open and well-understood architecture of the emerging Open MPI project is due to its modular design the most suitable implementation to incorporate ideas proposed in this paper. Thus, Open MPI is used to demonstrate and benchmark the results of the new approaches. Architectural and implementation details of the library are presented in chapter 1.4.

# 1.3 InfiniBand<sup>TM</sup>

The InfiniBand<sup>TM</sup> Architecture (IBA) is used as an interconnection network. It was mainly intended as a high speed interconnect for servers in a typical data center environment. The development process targeted at offering high bandwidth and high expandability for future computing systems and innovative features like RDMA and message send/receive within the user level without paying the costs for entering kernel routines. This, and the relatively low prices due to the wide spreading make InfiniBand<sup>TM</sup> also very attractive to HPC vendors. Especially the fact that the design actively supports standard busadaptions (e.g. PCI-X, PCI-Express<sup>TM</sup>, HTX) increases the suitability for clusters based on commodity components.

The InfiniBand<sup>TM</sup> specification [IBA] is actively developed and maintained by the Infiniband Trade Association (IBTA<sup>9</sup>). The first version of the specification was introduced in September 2000 as revision 1.0. Revision 1.1 followed after a subrevision 1.0.a (mainly error corrections) in June 2002 with some new features. The current revision 1.2, available since September 2004, introduces some new features proposed by different vendors (e.g. Mellanox<sup>10</sup>) such as a shared receive queue (see [IBA], section 10.2.9). The legacy revision 1.1 is used as a foundation for implementations and measurements because hardware fully supporting the specification 1.2 is not yet available. This denotes that all approaches shown in this work may be enhanced with features of the new specification.

## 1.3.1 InfiniBand<sup>TM</sup> Architecture

A deployed InfiniBand<sup>TM</sup> architecture is called a System Area Network. It consists of a number of switches which route packets based on virtual point-to-point connections. Nearly every device can act as an end point, beginning with a single I/O Terminal up to very complex systems such as multiprocessor computers. These systems are classified into two fields by their use cases. A TCA (Target Channel Adapter) usually fulfils exactly one task (e.g. a storage controller) while a HCA (Host Channel Adapter) acts together with a more complex system like a computer. The operation mode can additionally be divided into two connection variants:

- module-to-module (inter chip communication, if I/O modules are supported by the systems)

- chassis-to-chassis (classical host interconnect like Ethernet)

This paper assumes that the end-systems are normal computers and it uses the term HCA for the InfiniBand<sup>TM</sup> connection device. No further assumptions are taken for the connection parameters, both connection variants mentioned above are supported.

<sup>&</sup>lt;sup>2</sup>MPICH [http://www-unix.mcs.anl.gov/mpi/mpich]

<sup>&</sup>lt;sup>3</sup>LAM/MPI [http://www.lam-mpi.org]

<sup>&</sup>lt;sup>4</sup>Open MPI [http://www.open-mpi.org]

<sup>&</sup>lt;sup>5</sup>FT-MPI [http://icl.cs.utk.edu/ftmpi]

<sup>&</sup>lt;sup>6</sup>LA-MPI [http://public.lanl.gov/lampi]

<sup>&</sup>lt;sup>7</sup>LAM/MPI [http://www.lam-mpi.org]

<sup>&</sup>lt;sup>8</sup>PACX-MPI [http://www.hlrs.de/organization/pds/projects/pacx-mpi]

<sup>&</sup>lt;sup>9</sup>IBTA [http://www.infinibandta.org]

<sup>&</sup>lt;sup>10</sup>Mellanox [http://www.mellanox.com]

The IBA offers several features which are helpful for message passing. Some of them are listed in the following:

- reliable transport

- user level communication

- management infrastructure

- native IPv6

- decreased CPU utilization (full offloading)

- send/receive semantics and RDMA/Atomic

- scalability in bandwidth

- request queuing in hardware

- multicast

List 1.2: InfiniBand<sup>TM</sup> Features

## 1.3.2 Hardware Queuing

All requests are queued in hardware to ensure that multiple user-level applications can use the HCA to send or receive messages. Due to this fact, the operating system does not need to manage multiple accesses to the device. It acts as a normal entity requesting a service. Quality of Service (QoS), with several virtual lanes ordered by priority, may be used to ensure proper prioritization of data transmissions.

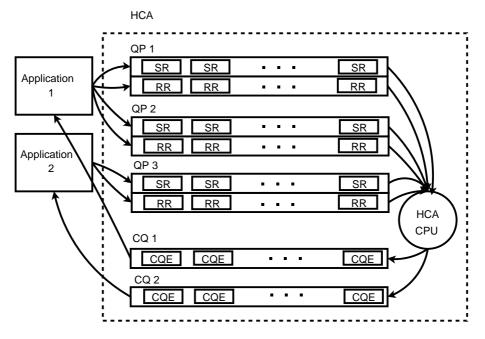

A queue is usually called Work Queue (WQ). Work Queues are created in pairs (Queue Pairs, QP), one for receive operations and one for send operations. Requests to send data (Send Requests, SR) to a remote node are posted to the Send Queue (SQ) and requests to receive data (Receive Requests, RR) with appropriate placement information are posted to the Receive Queue (RQ). The hardware fetches an element from the top of the queue and processes it. It has to be stated that two or more Work Requests (WR) can be processed in parallel, even if they originate from the same queue. The hardware places a notification with status information into a completion queue (CQ) associated with the source QP of the request after processing it. Whereby a completion queue can be shared between different Queue Pairs to simplify the use. Each application on the system creates several Queue Pairs for sending and receiving data, where usually every QP denotes a single communication channel to another system. The whole process is shown in figure 1.1.

A Send Queue can handle three different request types:

- 1. **SEND**

- 2. **RDMA**

- 3. MEMORY BIND

A SEND SR specifies a piece of data (address, length) in the local memory to send to a peer. The RDMA SR splits up into three modes:

- 1. **RDMA Write** specifies local data (address and length), a remote r\_key and a remote address to put the data

- 2. **RDMA Read** specifies a remote address, an r\_key and a length to fetch the data and a local address to put it

- 3. RDMA Atomic performs a 64 bit atomic read and a conditional modify in the remote memory

A MEMORY BIND WR instructs the hardware to change memory registration relations. The operation returns also a new r\_key which is used by foreign nodes to access local memory (see RDMA). The r\_key is a security feature to prevent undesired access to local memory by other nodes.

Figure 1.1: Hardware Queuing

A Receive Queue can only handle one type of Receive Request which specifies where to place the data which is received from another send operation on the remote side. Normal RDMA SR are usually not handled by Receive Queue Entries (RQE), except if the RDMA was issued with an 32 bit immediate value which consumes a RQE and puts the value into it.

## 1.3.3 Connection Management

The IBA supports connected and unconnected operation. The unconnected type uses datagrams to send and receive data and the connected type offers a virtual connection to send and receive (theoretically unlimited) streams of data. The segmentation and reassembly for connected types is done in hardware. To establish a connection, each partner has to create a QP and both have to tie them together. Each QP is uniquely addressed by the HCA LID (Local ID), optionally the GID (Global ID) and the local QP number. In comparison with the TCP/IP<sup>11</sup> protocol, the LID and GID correspond to the IP address (GID = network part, LID = host part) and the QP number correlates with the TCP port number. This information has to be exchanged in advance (e.g. through an out-of-band channel).

Unconnected QPs are not tied to a single remote node. The remote destination is given with each SQE. The same addressing scheme is used as for connected communication. This operation is expected to be generally slower than an already connected QP because most operations which are done during the connection establishment for connected QPs have to be repeated for each single packet.

## 1.3.4 Options for Message Passing

The IBA specification gives several options for passing a message from one system to another. One can use native IBA transport such as RDMA Read/Write, Send/Receive or other transport types like RAW Datagram encapsulating Ethernet or IPv6. The transport can be connection oriented or connectionless. Another choice is to use reliable transport or to handle the reliability in the application level. Table 1.1 shows a systematic list of service types and their related features.

<sup>&</sup>lt;sup>11</sup>Transmission Control Protocol/Internet Protocol

| Service Type               | Connection | Reliable | Send/Receive | RDMA | Transport |

|----------------------------|------------|----------|--------------|------|-----------|

| Reliable Connection (RC)   | У          | У        | У            | У    | IBA       |

| Unreliable Connection (UC) | У          | n        | У            | n    | IBA       |

| Reliable Datagram (RD)     | n          | У        | У            | у    | IBA       |

| Unreliable Datagram (UD)   | n          | n        | У            | n    | IBA       |

| RAW Datagram (RAW)         | n          | n        | у            | n    | RAW       |

## Table 1.1: InfiniBand<sup>TM</sup> Service Types

Each SQE has to fit to the QP regarding to the service type or it will be rejected. The following sections describe each of the IBA transport types to give a solid base for modelling the IBA and choosing the right connection type.

## 1.3.4.1 Reliable Connection (RC)

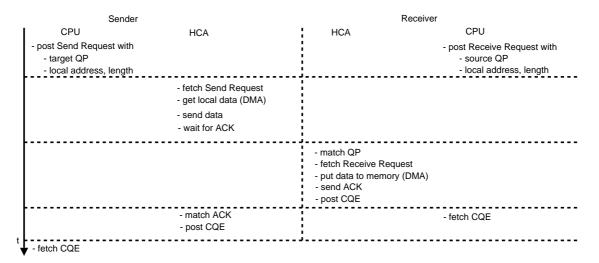

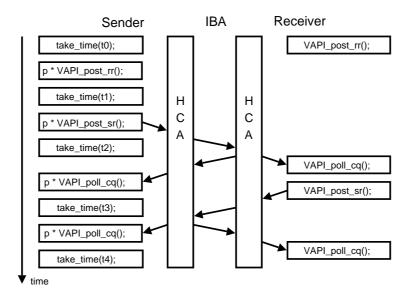

The steps for sending a message with the RC service type are shown in figure 1.2. It is assumed that the connection has been established in advance. The data is copied directly from the sender to the receiver's provided user-buffers (address, length) exploiting DMA functionality. Each message is acknowledged by transmitting an ACK packet back to the sender.

Figure 1.2: Reliable Connection

## 1.3.4.2 Unreliable Connection (UC)

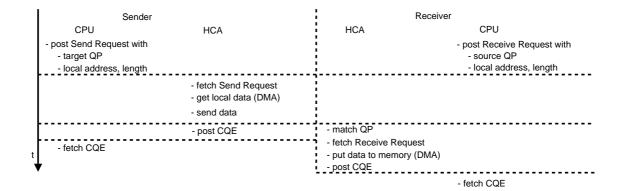

The process of sending a message with the UC service type is shown in figure 1.3. It is assumed that the connection has been established in advance.

## 1.3.4.3 Reliable, Unreliable and RAW Datagram (UD/RD/RAW)

The process of sending a message with RD or UD/RAW is nearly the same as for RC (figure 1.2) or UC (figure 1.3) respectively. Only one additional step of finding the route has to be added to the HCA tasks on the sender side before sending a packet. This leads to the conclusion that datagram sending is generally slower than sending packets over an already established connection.

Figure 1.3: Unreliable Connection

#### 1.3.5Interacting with the HCA

All actions to send or receive data between the user process and the HCA are fully done in the user space of the operating system. The standard defines a so called verbs which is not a programming interface (API), but which defines necessary elements of an API so that the operating system vendor can develop his own version of the verbs API to interact with user programs. This means that verbs is a semantical description of functions which have to be offered to the user. This freedom resulted in mainly three different types of available verbs APIs, the Mellanox verbs API and the SF-IBAL verbs API. Both have been combined into the new emerging standard of the OpenIB verbs API. The  $OpenIB^{12}$  initiative was founded by different vendors to specify a standard API for accessing the HCA verbs. Due to this standardization efforts, all verbs API examples are shown with the Mellanox VAPI<sup>13</sup> which is fully compatible with the new OpenIB API. More functions have been defined by Mellanox in addition to the standard and are called EVAPI<sup>14</sup>. Some of them are used in the source codes but they are also fully supported by the OpenIB API. The necessary VAPI calls to establish a connection and send a message between two nodes are shown in the following list (simplified). Both nodes perform equal actions for initialization and connection establishment. The only difference resides in the last call to VAPI\_post\_sr(QP) to post a Send Request (on the sender side) or VAPI\_post\_rr(QP) to post a Receive Request (on the receiver side). All memory to send or receive data has to be registered in advance to indicate the HCA the user buffer regions. The register operation locks the pages in memory so that a DMA access from the HCA can be guaranteed at any time.

- 1. VAPI\_open\_hca() inits the HCA

- 2. VAPI\_alloc\_pd() offers additional memory access rights (if more than one  $PD^{15}$  is allocated)

- 3. VAPI\_create\_cq() creates a new CQ

- 4. VAPI\_register\_mr(ADDR, LEN) registers memory to send or receive data

- 5. VAPI\_create\_qp(QP) creates a new Queue Pair

- 6. VAPI\_modify\_qp(RST->INIT) modifies QP from Reset (RST) to Init

- 7. VAPI\_modify\_qp(INIT->RTR, LID, QP\_NUM) modifies QP from Init to Ready to Receive (RTR)

- 8. VAPI\_modify\_qp(RTR->RTS) modifies QP from RTR to Ready to Send (RTS)

- 9. VAPI\_post\_sr(QP) posts a Send Request to SQ (Sender)

- 10. VAPI\_post\_rr(QP) posts a Receive Request to RQ (Receiver)

<sup>11.</sup> VAPI\_poll\_cq(CQ) - polls completion queue for new entries

<sup>&</sup>lt;sup>12</sup>OpenIB [http://www.openib.org]

$<sup>^{13}</sup>$ verbs API

$<sup>^{14}</sup>$ Extended verbs API  $^{15}$ Protection Domain

- 12. VAPI\_deregister\_mr() deregisters memory

- 13. VAPI\_destroy\_qp(QP) destroys QP in HCA

- 14. VAPI\_destroy\_cq(CQ) destroys CQ in HCA

- 15. VAPI\_dealloc\_pd(PD) destroys PD

- 16. VAPI\_close\_hca(HCA) closes HCA

A full list of VAPI/EVAPI functions is available from Mellanox or the OpenIB project.

## 1.4 Open MPI

Open MPI, presented in [GFB<sup>+</sup>04], is chosen as a framework to incorporate the algorithms, mainly because of its open and extensible framework. Incorporating new collective algorithms is fairly easy. The architecture of Open MPI will be briefly described in the following. However, Open MPI undergoes heavy development including the architecture which had recently major changes and it is not possible to know if more things will be changed in the future. So this description has to be seen to be linked to the current prerelease state of the art.

## 1.4.1 Component Framework

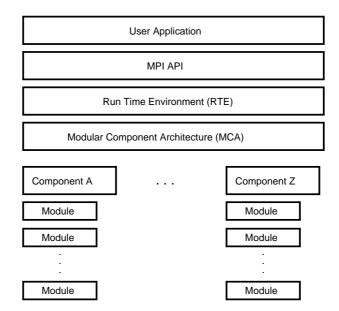

The architecture of Open MPI, described in [GFB<sup>+</sup>04] and [SL04] changed slightly and resulted in three distinct software layers:

- 1. MPI MPI Layer

- 2. **RTE** Run Time Environment

- 3. MCA Modular Component Architecture

The MPI Layer is the adaption layer integrating the MPI standard into the underlying functionality (mainly the RTE and the MCA). The RTE layer provides services at run time (e.g. process startup or output forwarding). These layers do not have to be modified to incorporate new collective algorithms, so there is no need to investigate them further.

The MCA layer is a component framework, called Modular Component Architecture (formerly MPI Component Architecture). This framework manages other layers below by providing several services (e.g. finding components or processing user parameters). Each major functional area has an associated component framework to manage multiple components performing related or identical tasks. Each component is clearly defined by an interface and offers functional services to the upper layers of the framework. An initialized component is called a module and can be seen as an instance of the associated component.

The framework with all layers, some example component frameworks (components A and Z) and managed modules is shown in figure 1.4.

The next listing shows a number of frameworks already implemented in Open MPI. However, the architecture is flexible enough to add arbitrary functionality with new frameworks.

- **PTL** The Point-to-point Transport Layer consists of network specific modules responsible for low level data transfer. It can be seen as a kind of device driver.

- **PML** The Point-to-point Management Layer provides several transport services for the MPI Layer (e.g. segmentation and reassembly, striping or reliability).

- COLL The Collective framework provides modules for collective operations.

- **TOPO** The Topology framework offers processes running within an MPI job a facility which allows the MPI library components to perform optimizations based on locality (e.g. in grid environments).

List 1.3: Available Open MPI Component Frameworks

Figure 1.4: Open MPI Architecture

COLL is the most essential framework for this paper. The others are not investigated any further. To understand the structure of a single COLL component, the general structure of a component has to be described.

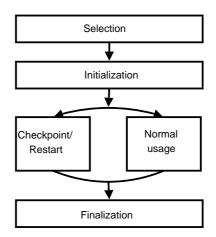

## 1.4.2 A Components Lifecycle

As described in [SL04], a component runs through five stages during its existence within the MCA: Selection, initialization, checkpoint/restart, normal operation and finalization. Figure 1.5 shows the order in which these stages are traversed. The COLL component is called module after initialization because each communicator is associated with a single COLL module (but all of these share the same source code). This means that only one instance of the COLL component offering a specific functionality can be active at any time, but each communicator has its own state (comparable to an instance) of this module.

Figure 1.5: A Components Lifecycle

The "selection" is done during the creation of a new communicator (including MPI\_COMM\_WORLD and MPI\_COMM\_SELF), typically triggered inside the MPI API functions MPI\_INIT, MPI\_COMM\_CREATE, MPI\_COMM\_DUP, MPI\_COMM\_COMMIT or MPI\_COMM\_SPLIT. The mca\_coll\_<name>\_comm\_query function of

MPI\_COMM\_DUP, MPI\_COMM\_COMMIT or MPI\_COMM\_SPLIT. The mca\_coll\_<name>\_comm\_query function of each available component is queried by the framework to return a list of function pointers to the offered

functions and a priority (between 0 and 100). The initialization function is also used to test the availability of special features inside the created communicator. If a required feature (e.g. an InfiniBand<sup>TM</sup> connection to all nodes) is not available, the component can simply disable itself by returning a null pointer. The component returning the highest priority is selected by the COLL framework.

The winning component enters the "initialization" phase and the COLL framework calls the mca\_coll\_<name>\_module\_init function. The component can also initialize internal data structures, hardware features or any other one-time-setup which is necessary to use the collective functions later on.

The initialized data has to be associated with the communicator structure by changing the

$c\_coll\_basic\_data$  pointer to the beginning of the data structure. The component returns a pointer at the framework which includes a list to all provided functions after the initialization work is done. If several functions are not supported, the function pointers should be null to indicate to the COLL framework that the basic functions (provided by a component named basic) should be used. The proposed module contains only the barrier function (null pointers for all other functions) and uses the initialization phase to perform the barrier setup phase which has to be done only once at startup. The relevant information is stored in a structure which is referenced by the  $c\_coll\_basic\_data$  pointer.

The "checkpoint/restart" stage has to take care of messages which are currently on the fly and has to drain all queues. This is not required in our case because the component is layered on top of the PTL interface for sending and receiving messages (PTL takes care itself).

"Normal usage" is the state where requested collective operations (e.g. MPI\_Barrier()) are performed. Therefore previously stored data may be extracted from the communicator. The functions are called by their function pointers which were provided to the COLL during the initialization phase.

The finalization step requests the module to clean up all used data structures and drain the network to unload cleanly. The function mca\_coll\_<name>\_module\_finalize is called to trigger the cleanup.

## 1.5 Summary

This chapter gave an introductory description of the basics for this thesis. The MPI Standard, the InfiniBand<sup>TM</sup> network and the Open MPI framework was described in all facings which are relevant for the reminder of this paper. The following chapter analyzes the possibilities to implement the barrier functionality in software.

# Chapter 2

# Software Solution

Implementing collective algorithms in hardware or in software are the two fundamental paradigms to optimize them. The latter possibility will be analyzed first. The software algorithm can be layered on top of normal message passing operations, without modifying the hardware design or adding new components. This approach can be generally considered as cheaper in terms of production costs and is more portable across different systems with the same underlying communication architecture. There are several well known algorithms which are currently used to perform the barrier by using normal MPI point-to-point operations on top of any message passing system. Most of them were developed for shared memory systems and have been adopted to distributed memory systems (like InfiniBand<sup>TM</sup>). These algorithms are evaluated regarding to their running time and scalability (time to complete the barrier operation when all n nodes reach the barrier simultaneously). To perform these evaluations in a proper and accurate way, a model of the underlying network (in our case InfiniBand<sup>TM</sup>) has to be found or developed if there is no suitable model available yet. The section 2.1 will investigate different models for parallel computation on distributed memory systems. Section 2.2 evaluates all currently known algorithms regarding to the chosen model and draws a conclusion to implement a single algorithm for performing the barrier operation.

## 2.1 Models for Parallel Computation

## 2.1.1 Introduction

The different barrier algorithms have to be modeled to find the optimal solution of the problem for the InfiniBand<sup>TM</sup> network. The used model should reflect the network properties as accurate as possible. The following section describes several models which could be used to analyze barrier algorithms and predict the runtime behavior. The most accurate model is chosen as a result.

Models for parallel programming are often used to develop and optimize time critical sections of algorithms for parallel systems. These models should reflect all relevant parts of real-life-systems for algorithmic design. Several simplifying assumptions are taken to create these models. The next part of this thesis deals with analysis and evaluation of different well known models for their suitability to the InfiniBand<sup>TM</sup> network architecture. All models are described and rated<sup>1</sup> in this work.

## 2.1.2 Related Work

Many models have been developed during the past years. Most of them are dedicated to a specific hardware or network architecture [Lei92, Ble87] or the shared memory paradigm [LCW93, GMR97]. There are also some general purpose parallel models which try to remain architecture independent like the PRAM [FW78b, KR90], the BSP [Val90], the  $C^3$  [HK94] or the LogP [CKP<sup>+</sup>93] model. These generic

<sup>&</sup>lt;sup>1</sup>rating is done by comparing advantages and disadvantages for modeling InfiniBand<sup>TM</sup>

programming models are characterized and used as starting point for further work. Several comparative studies and surveys are also available [MMT95, Ham96, BHP96], but they provide a limited view by comparing just a small subset of all available models.

## 2.1.3 Organization

Each mentioned model is described by its main characteristics. A reference to the original publication is given for additional details (e.g. detailed information in terms of execution time estimation). Each model is analyzed in advantages and disadvantages for modeling the InfiniBand<sup>TM</sup> architecture, and a conclusion for further usage in the design process of a new model is drawn. Several models have been enhanced by different modifications of third authors. Some of them and their implications for the usability of the underlying model are discussed in a separate subsection. The last section draws a conclusion and proposes a suitable model for the barrier operation over the InfiniBand<sup>TM</sup> network.

## 2.1.4 Characterization of available Models

## 2.1.4.1 The PRAM Model

The PRAM model was proposed by Fortune et al. in 1978 (see [FW78a]). It is the simplest parallel programming model known. But there are some serious defects in its accuracy. It was mainly derived from the RAM model, which bases itself on the "Von Neumann" model [vN45]. It is characterized by P processors sharing a common global memory. Thus it can be seen as a MIMD<sup>2</sup> machine. It is assumed that all processors run synchronously (e.g. with a central clock) and that every processor can access an arbitrary memory location in one step. All costs for parallelization are ignored, thus the model provides a benchmark for the ideal parallel complexity of an algorithm.

#### 2.1.4.1.1 Evaluation

The main advantage is the ease of applicability. To reach this simplicity, several disadvantages have to be accepted. The main drawbacks are that all processors are assumed to work synchronously, the interprocessor communication is free<sup>3</sup> and it neglects the contention when different cells in one memory module are accessed.

Thus, this model is not suitable for any synchronization algorithm because interprocessor communication is free.

#### 2.1.4.1.2 Additions to the PRAM Model

There are numerous additions to the PRAM model addressing its main disadvantages. The Module Parallel Computer (MPC [MV84]) consists of n memory modules with a specific size, where each module can be accessed by only one processor simultaneously. This models the memory bank contention in current multiprocessor systems. Other extensions [CZ89, Gib89] are modeling the natural asynchronity of current systems. The latency of write operations to non-local memory are modeled in the LPRAM [ACS90] or the BPRAM [ACS89] but they do match the properties of today's message passing based clusters<sup>4</sup>. Also the bandwidth is modeled for PRAM in the DRAM model [LM88]. But the problem of the unification of all different models, from which each model addresses a specific disadvantage, is still remaining. Thus, no single addition to the PRAM is suitable to satisfy the needs of modeling the InfiniBand<sup>TM</sup> architecture sufficiently.

$<sup>^2\</sup>mathrm{Multiple}$  Instruction Multiple Data

$<sup>^{3}</sup>$ zero latency, infinite bandwidth leads to excessive fine-grained algorithms

<sup>&</sup>lt;sup>4</sup>e.g. block-transfers are not possible, the latency is charged for each byte

## 2.1.4.2 The BSP Model

The Bulk Synchronous Parallel (BSP) model was proposed by Valiant in 1990 [Val90]. The BSP model divides the algorithm into several consecutive supersteps. Each superstep consists of a computation phase and a communication phase. All processors start synchronously at the beginning of each superstep. In the computation phase, the processor can only perform calculation on data inside its local memory<sup>5</sup>. The processor can exchange data with other nodes in the communication phase. Each processor may send at most h messages and receive at most h messages of a fixed size in each superstep. This is called a h-relation, further on. A cost of  $g \cdot h$  (g is a bandwidth parameter) is charged for the communication.

#### 2.1.4.2.1 Evaluation

Latency and (limited) bandwidth are modeled as well as asynchronous progress per processor. A big disadvantage for modelling barrier operations is the fact that the BSP also assumes special synchronization hardware (barrier is done in O(1)). Additionally, each superstep must be long enough to send and receive the h messages<sup>6</sup>, resulting in some nodes being idle at the end of a superstep. This leads to the problem that messages received in a superstep cannot be used in the same superstep even if the latency is smaller than the remaining superstep length.

Because of the implicit synchronization, the BSP model is not suitable for modelling barrier algorithms. Each superstep begins in a globally synchronous state.

## 2.1.4.3 The $C^3$ Model

The  $C^3$  model, proposed by Hambrusch et al in 1994 [HK94], was also developed for coarse grained supercomputers. The model works also by partitioning an algorithm into several supersteps. Each superstep consists of local computation followed by communication. Supersteps start synchronously directly after the preceding superstep is finished, this implies that a barrier without any costs is necessary (see also the BSP model in chapter 2.1.4.2).

#### 2.1.4.3.1 Evaluation

The  $C^3$  model evaluates complexity of communication, computation and congestion of the interconnect for coarse grained machines. Store-and-forward, as well as cut-through routing can be modeled and the difference between blocking and non-blocking receives is also considered.

But the disadvantages overbalance. The most significant drawback, which prevents the usage of the model for barrier synchronization, is the assumption that a barrier costs nothing and is implicit. Thus, the barrier would be modeled as a single empty superstep which makes no sense (see also section 2.1.4.2). Other drawbacks are that the message exchange can be performed only in fixed length packets and that the clock speed and bandwidth parameters are not included, so that the model is only valid when the processor bandwidth and the network bandwidth are equal<sup>7</sup>. Due to these facts, this model cannot be used for barrier operation over InfiniBand<sup>TM</sup> networks and is not investigated further on.

## 2.1.4.4 The LogP Model

The LogP model  $[CKP^+93]$  was proposed by Culler et al. in 1993. It was developed in addition to the PRAM model (see chapter 2.1.4.1) to cover the changed conditions for parallel computing. It reflects different aspects of coarse grained machines which are seen as a collection of complete computers, each consisting of one or more processors, cache, main memory and a network interconnect<sup>8</sup>.

<sup>&</sup>lt;sup>5</sup> if this is data from remote nodes, it has been received in one of the previous supersteps

<sup>&</sup>lt;sup>6</sup>the greatest h among all nodes!

<sup>&</sup>lt;sup>7</sup>e.g. Intel Touchstone Delta

$<sup>^{8}\</sup>mathrm{e.g.}$  the Intel Delta or Paragon, Thinking Machines CM-5 ...

It is based on four main parameters:

- L communication delay (**upper** boundary to the latency for NIC-to-NIC messages from one processor to another)

- o communication overhead (time that a processor is engaged in transmission or reception of a single message)

- g gap (indirect communication bandwidth, minimum interval between consecutive messages,  $bandwidth \sim \frac{1}{a}$ )

- *P* number of processors

#### List 2.4: The four parameters of the LogP model

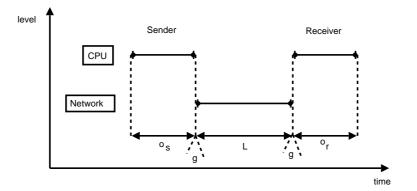

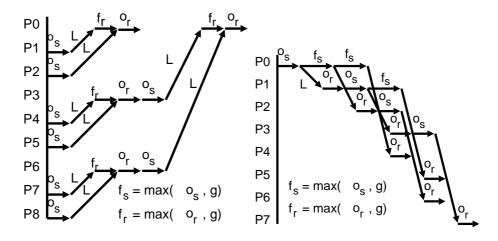

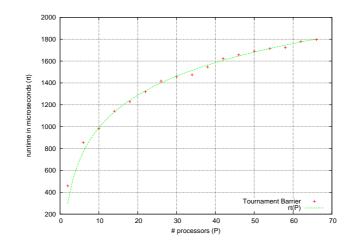

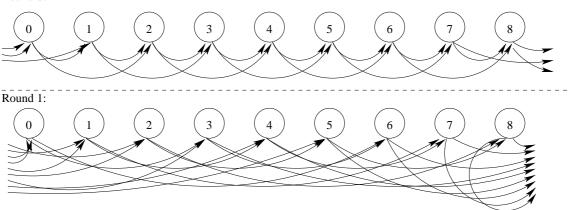

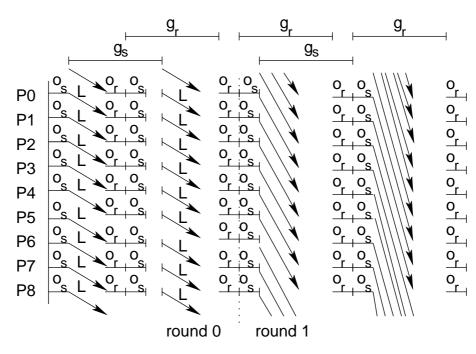

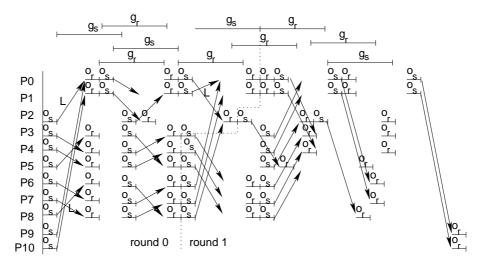

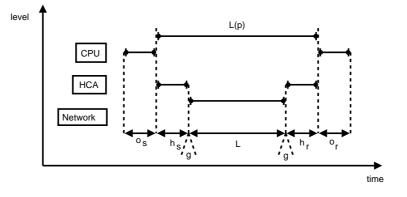

The parameters of the LogP model can be divided into two layers, the CPU-Layer and the Network-Layer. The o-parameter can also be subdivided into one parameter on the receiver side  $(o_r)$  and another on the sender side  $(o_s)$ . The according visualization of the different parameters for a given network (e.g. Ethernet) can be seen in Figure 2.1.

Figure 2.1: Visualization of the LogP parameters

There are several implicit assumptions taken with these four parameters to make the model fully functional:

- $\lceil \frac{L}{g} \rceil$  count of messages that can be in transmission on the network from one to any other processor in parallel

- L, o and g are measured as multiples of the processor's clock speed

List 2.5: Additional assumptions in the LogP model

It is easy to understand that developing and programming in the PRAM model is easier than in the LogP model, but the bigger accuracy of this model should justify the additional effort. There were also some investigations to find upper bounds to the execution time for PRAM based algorithms on LogP (coarse grained) machines [LZ95] which can be used to simplify the programming again, but they are not suitable for synchronization algorithms (see 2.1.4.1).

An additional study [CLMY96] describes options of assessing the network parameters for real-life supercomputers. This can be very helpful to gain a deeper knowledge about the model's characteristics.

#### 2.1.4.4.1 Evaluation

The LogP model has several advantages over other models. It is designed for distributed memory processors and the fact that network speed<sup>9</sup> is far smaller than CPU speed. It is easily applicable for a flat network model<sup>10</sup>. It encourages careful distribution of computation and overlapping communication as

<sup>&</sup>lt;sup>9</sup>this means latency as well as bandwidth

<sup>&</sup>lt;sup>10</sup>central switch based, diameter = 1

well as balanced network operations<sup>11</sup> which is very profitable for determining the running time of many applications accurately.

Some small drawbacks are that the whole communication model consists only of point-to-point messages. This does not respect the fact that some networks (especially InfiniBand<sup>TM</sup>) are able to perform collective operations (e.g. multicast) ideally in O(1). The second drawback is that only short fixed-size messages are modeled, but this can be ignored for the barrier problem.

#### 2.1.4.4.2 Additions to the LogP Model

The LogP model seems to be very promising, thus the additions to the model are examined more in-depth than for the other models.

#### 2.1.4.4.3 LogGP - Long Messages in LogP

The LogGP model was proposed by Alexandrov et al. in 1995 [AISS95]. It was meant as an addition to the original LogP model to address its inaccuracy for bigger messages. The LogP model is only suitable for small fixed size messages, because it uses the inter-frame gap g to express the bandwidth indirectly  $(bw \sim \frac{1}{g})$ . However, this ignores the fact that many modern interconnect technologies have special support for providing a much higher bandwidth for long messages<sup>12</sup>. The LogGP model incorporates the new parameter G into the original model to pay attention to this fact.

This extension will not be investigated any further because there is no necessity for long messages in the barrier functionality<sup>13</sup>.

#### 2.1.4.4.4 LoGPC - Modelling Network Contention

The traditional LogP model is only correct if no network contention occurs. But this assumption is (especially for n-cube networks) not very accurate. Therefore the LoGPC model [MF01] proposes a new technique to incorporate network contention and the pipelining characteristics of the DMA engine into the LogP model. The model was developed for k-ary n-cube networks [Aga91]. The author predicts that the model is easily applicable to other network topologies by changing a single parameter, but this seems not very precise for a central-switch based architecture.

This extension is quite interesting, but seems to be not adaptable to the special needs of a central-switch based InfiniBand<sup>TM</sup> network, because a k-ary n-cube network is not able to behave like a central switch based architecture.

#### 2.1.4.4.5 LogGPS - Modelling Synchronization

The LogGPS model [IFH01] incorporates an additional delay which is caused by several MPI [For95] libraries due to the rendezvous protocol which is used for sending long messages. The synchronization overhead caused by the rendezvous protocol is modeled with the additional parameter S.

This model is only necessary for long messages sent through the MPI layer. Thus this model will not be investigated any further.

## 2.1.4.5 Choosing a Model

As described in 2.1, the LogP model is the most accurate model in this specific case. Thus, it is used for all running time estimations in the following sections.

Several simplifying architectural assumptions can be made without lowering the asymptotical accuracy of the model heavily.

<sup>&</sup>lt;sup>11</sup>no single processor is "flooded"

<sup>&</sup>lt;sup>12</sup>e.g. by pipelining or bulk transfers

<sup>&</sup>lt;sup>13</sup>even zero-byte messages are sufficient to notify the status to other nodes

Based on the fact that most clusters operate a central switch connecting all nodes, the properties of this interconnect can be assumed as follows:

- full bisectional bandwidth

- full duplex operation (parallel send/receive)

- the forwarding rate is unlimited and packets are forwarded in a non-blocking manner

- the latency (L from LogP model) is constant above all messages

- the gap between consecutive messages is much smaller than the overhead to process a message on the host system  $\Rightarrow g$  from LogP is much smaller than o and so overlaid while sending multiple messages (see section 3.1 in [CKP<sup>+</sup>93])

- the overhead (o) is constant for single messages (for simplicity:  $o_s = o_r = o$ )

List 2.6: Interconnect characteristics

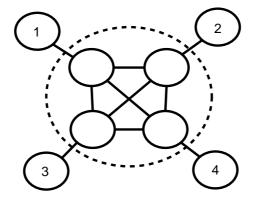

Figure 2.2: The ideal interconnect graph connecting 4 nodes

This model can be described as a graph where all nodes are connected to a fully meshed network. An example is shown in figure 2.2. A nearly ideal interconnect architecture can be manufactured by using the crossbar switch model, depicted in figure 2.3. This model is widely used to produce actually available switches.

Figure 2.3: A crossbar example connecting 4 nodes

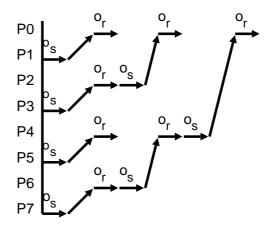

The pedantic communication characteristics are defined as follows: The time to send and receive a single message<sup>14</sup> can be approximated to  $o_s + L + o_r$ , and the time to send n messages<sup>15</sup> can be estimated as  $o_s + (n-1)max\{o_s,g\}^{16}$ . The time to receive n messages (relative to the first packet sent on the sender side) can be modeled as  $o_s + L + o_r + (n-1)max\{o_s,g\}$ .

<sup>141:1</sup> communication

$<sup>{}^{15}\</sup>mathrm{1}:n$  communication with enqueuing

<sup>&</sup>lt;sup>16</sup>the time  $o_s$  and g can run in parallel

Additionally, some constructs show up frequently and are defined as follows:

$$f_{r} = max\{o_{r}, g\}$$

$$f_{s} = max\{o_{s}, g\}$$

$$t_{r} = max\{f_{r}, o_{s} + L + o_{r}\}$$

$$= max\{max\{g, o_{r}\}, o_{s} + L + o_{r}\}$$

$$= max\{g, o_{s} + L + o_{r}\}$$

$$t_{s} = max\{f_{s}, o_{s} + L + o_{r}\}$$

$$= max\{max\{g, o_{s}\}, o_{s} + L + o_{r}\}$$

$$= max\{g, o_{s} + L + o_{r}\}$$

With the aforementioned assumptions follows

$$f_r = f_s = o$$

$$t_r = t_s = 2o + L$$

This paper distinguishes between  $t_r$  and  $t_s$  in order to emphasize the semantic properties of the algorithms being analyzed.

## 2.2 Barrier Algorithms

After defining the model which can be used for analyzing barrier algorithms, the following section describes all presently published algorithms and their asymptotic behavior for increasing processor counts. The LogP model is used to predict the asymptotic runtime behavior. The simplifying assumptions named in section 2.1.4.5 are taken for all further predictions.

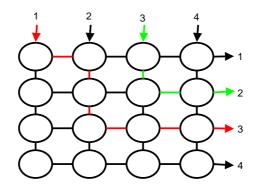

The best way to understand each algorithm is to read the description in combination with the given graphical representation. To gain further knowledge about the algorithms, especially on message passing based systems, the reader is encouraged to retrace the proposed pseudo-code.

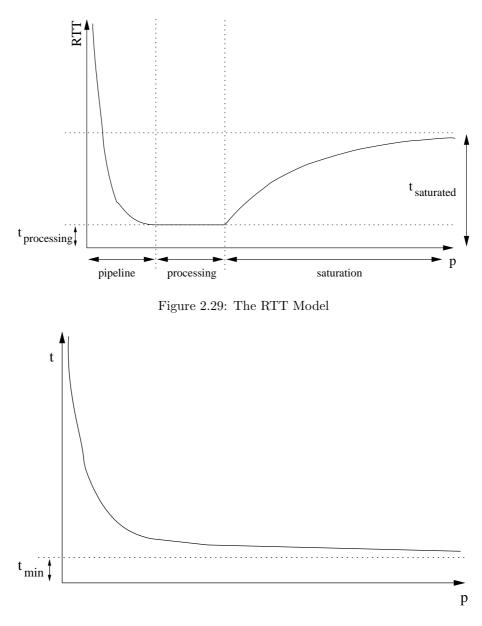

The following sections introduce all currently known barrier algorithms. Each algorithm can be split up logically into three phases. The algorithm is initialized in phase 1 (e.g. reserving shared objects or calculating ranks). So it has to be done only once during initialization or reconfiguration (processors enter or leave) of each communicator. Phase 2, also called "Check-in-Phase" has to be done on each node every time when it calls MPI\_Barrier. All nodes communicate with each other until one or all nodes know that every node reached its MPI\_Barrier call. A barrier-identifier is often used to distinguish between different MPI\_Barrier calls to avoid race conditions when one processor enters the next barrier before all other processors left the last barrier - this is called x in the following chapter. Each barrier number is used once per communicator and incremented for each barrier starting initially with 1. The third and last phase can be referred to as "Notification-Phase" and is only needed when not all processors know that the barrier has been reached by each member of the communicator. The typical case is that one processor knows that the barrier is reached by each member of its communicator and it has to notify all remaining processors. The difference in phase 3 leads to a distinction between two types of algorithms. The first type performs phase 3 as described above (see section 2.2.1) and the second type omits it completely (see section 2.2.2 on page 28). Section 2.2.3 summarizes all algorithms for future analysis and provides simplified information about running time and memory usage relative to the processor count P. A proof of optimality is given in section 2.2.4 followed by a classification of the algorithms in four complexity groups (section 2.3.5), regarding to the LogP model. One representative of each group is analyzed more in detail for the runtime and the asymptotical behavior is compared to a practical benchmark result. Basing on this comprehensive analysis, two new algorithms which efficiently utilize hardware parallelism are proposed in section 2.2.6 and modeled in the LogP model. The running time for all algorithms is assessed under the assumption that the LogP model is accurate for the underlying network and that all nodes arrive simultaneously in their MPI\_Barrier() call (balanced case).

## 2.2.1 Algorithms Performing Phase 3

Phase 3, as described in Section 2.2 can efficiently be implemented as a broadcast (e.g. MPI\_Bcast). This operation could especially benefit from hardware broadcast or multicast capabilities which perform (ideally) in O(1). If this is not capable with the underlying architecture<sup>17</sup>, standard broadcast algorithms could be used, which usually scale with O(log(P)) for 1 byte messages. The time which is necessary to perform a broadcast from one to n nodes is modeled as  $t_{bc}(P)$  regardless of the implementation and architectural details mentioned above.

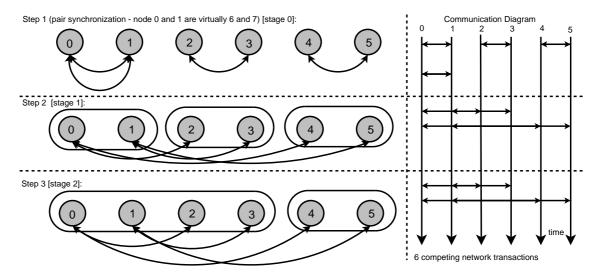

#### 2.2.1.1 Central Counter

#### 2.2.1.1.1 Description

This algorithm is quite simple and straightforward. Because of its obvious simplicity and the naive prove for correctness it is implemented quite often. Especially the atomic "fetch-and- $\Phi$ "<sup>18</sup> operation is frequently mentioned related to this barrier. This approach is investigated for the fetch-and-increment<sup>19</sup> operation in [FG91] and [GVW89]. One node holds an integer value which is used as central barrier counter. This integer starts with 0 and is increased by each node once (after it entered the barrier) until the node count P is reached. The last node sends a message to all other nodes to activate them.

This barrier consists of the two parts counting and notification. Both parts can be optimized independently. Optimized algorithms for counting and broadcasting a message are evaluated later. We assume the easiest case in the following pseudo-code (see listing 2.1) and graphical representation (see figure 2.4).

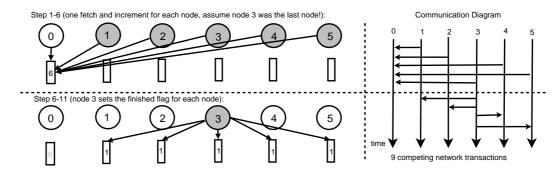

Figure 2.4: A Central Counter barrier between 6 nodes

#### 2.2.1.1.2 Conclusion

As the algorithm splits up into two phases for each MPI\_Barrier call, each phase is analyzed apart. Phase one is critical, because the shared counter is altered by each node. This memory location is called a hot-spot [PN85]. P - 1 competing network transfers are needed to implement the counter and the running time would be  $L + P \cdot o$ . These operations have to be atomic on the target to prevent lost-update problems, resulting in deadlocks. Phase two is also critical, because one node has to inform all other nodes. Phase one disturbs the transaction scheduling of the memory controller. Regarding to 2.2.1, the possibilities to perform this broadcast are not mentioned here. Thus, the overall running time of this operations can be seen as  $L + P \cdot o + t_{bc}(P - 1)$ . The memory usage is constant (1 byte) per node.

<sup>&</sup>lt;sup>17</sup>regardless if it's provided by hardware or software

<sup>18</sup>" fetch-and- $\Phi$ " is a conceptional term for a collection of atomic operations which change and return a single value in memory - for example fetch-and-add, fetch-and-swap, fetch-and-inc, ...

<sup>&</sup>lt;sup>19</sup>the fetch-and-increment operation takes a value to increment from its caller, increments its memory value and returns the new value to the caller (some implementations may return the value before incrementing)

```

// parameters (given by environment)

set p = number of participating processors

set rank = my local id

5

// phase 1 - initialization (only once)

set x = 0 // the barrier counter

if rank == 0 then

// its my counter

reserve ctr with 1 entry as shared

10

set ctr = 1

else

reserve flag with 1 entry as shared

set flag = 0

ifend

15

// phase 2/3 - central barrier

set x = x + 1;

if rank == 0 then

wait until ctr == p

20

else

set localctr = fetch and increment ctr on node 0

if localctr == p then

set flag in all nodes to x

ifend

25

wait until flag >= x

ifend

```

Listing 2.1: Central Counter in Pseudocode

## 2.2.1.2 Combining Tree

## 2.2.1.2.1 Description

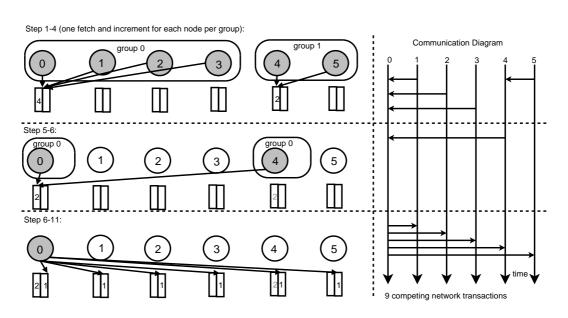

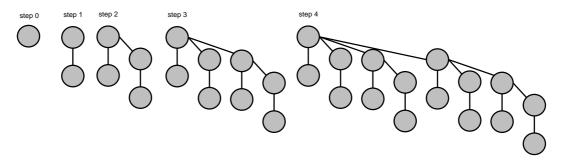

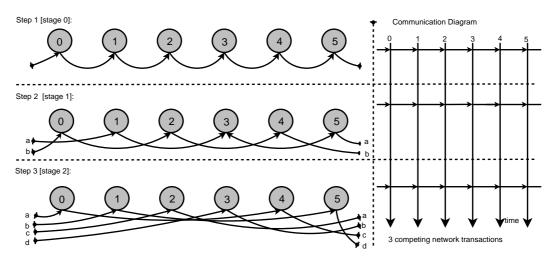

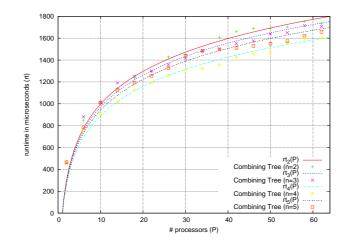

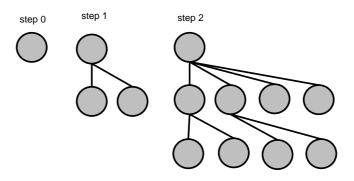

The combining tree barrier was introduced by Yew, Tzeng and Lawrie in [YTL87]. It uses a tree to speed up the central counter barrier. It divides the nodes into subgroups with n members, which synchronize among each other with a simple shared counter. Every first node of each group spins<sup>20</sup> its local counter which is shared to all others until all nodes reach the barrier (*counter* == n). When all nodes in the subgroup reached the barrier, all first nodes form a new group and synchronize among each other. This is repeated until only one group is left and has finished the synchronization. The first node informs all other nodes about the barrier completion. Yew reported a group-count (n) of 4 to achieve the best results. A graphical example as well as pseudocode for this algorithm can be found in figure 2.5 and listing 2.2.

## 2.2.1.2.2 Conclusion

The combining tree barrier reduces hot spots in memory and network contention. The number of required network operations is naively seen lowered to  $log_n P$  steps<sup>21</sup>. But due to enqueuing during the receive, the actual execution time under the assumption of the LogP model is  $(L + n \cdot o) \cdot \lceil log_n P \rceil + t_{bc}(P - 1)$  and 2 bytes of memory are used per node.

$<sup>^{20}</sup>$ check the counter frequently

$<sup>^{21}</sup>$ this is only valid for a fan-out of n - e.g. in a mesh topology, it has to be seen as a naive approximation for all other cases

Figure 2.5: A combining tree barrier between 6 nodes

```

set p = number of participating processors

set n = nodes per group // parameter

set rank = my local id

// phase 1 - initialization (only once)

5

set x = 0 // the barrier counter

reserve ctr with 1 entries as shared

set ctr = 1

reserve flag with 1 entries as shared

10

set flag = 0

set round = 0 // actual round

set relnodeid = 0 // relative nodeid (only active nodes)

15

// phase 2 - barrier

set x = x + 1;

repeat

set round = round + 1

set relnodeid = rank / (n<sup>(round-1)</sup>)

20

set grpnum = relnodeid div n // group number?

set grprank = relnodeid mod n // my rank in group

// I am out of the game, when I have no

// natural number as relnodeid

25

if round(relnodeid) != relnodeid then

wait until flag >= x

ifend

if grprank == 0 then

30

wait until ctr == n

else

set ctr = fetch and increment ctr on node \setminus

rank-grprank*n^(round-1)

wait until flag >= x

35

ifend

until round = \log(n)(p) or flag > x

// phase 3

if rank == 0 then

40

set flag in all other nodes to \boldsymbol{x}

ifend

```

Listing 2.2: Pseudocode for Combining Tree Algorithm

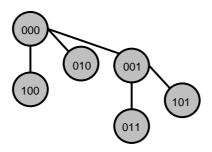

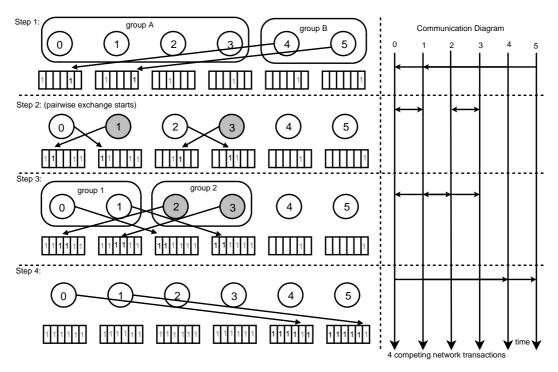

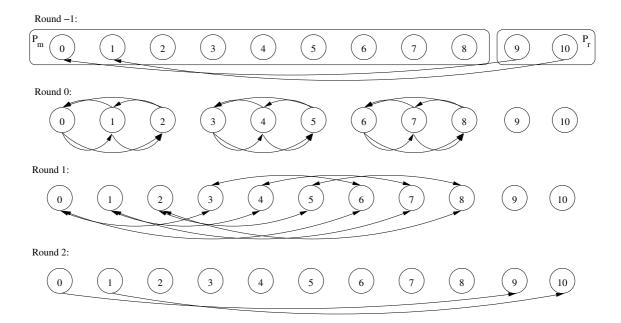

## 2.2.1.3 Tournament

#### 2.2.1.3.1 Description

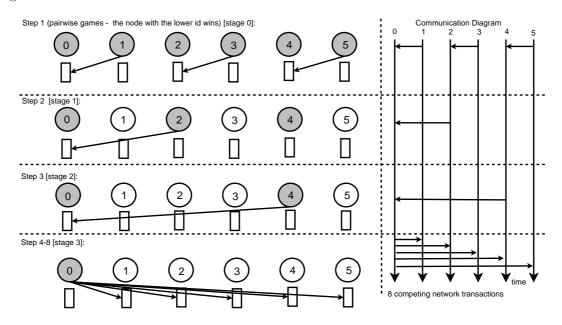

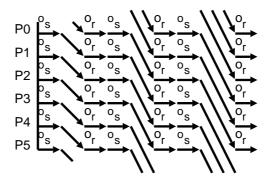

The Tournament Barrier, proposed by Hengsen et al. in [HFM88] is mostly suitable for shared memory multiprocessors because it benefits from several caching mechanisms. Nevertheless, the algorithm is analyzed here. As in the Butterfly (see chapter 2.2.2.1) and the Dissemination Barrier (see chapter 2.2.2.3), different rounds are used. The algorithm is similar to a tournament game. In each round two nodes play against each other. The winner is known in advance and waits until the looser arrives. The winners play against each other in the next round. The overall winner (the champion) notifies all others about the end of the barrier. A graphical and pseudo-code representation can be found in figure 2.6 and listing 2.3.

Figure 2.6: Example for the tournament barrier with 6 nodes

#### 2.2.1.3.2 Conclusion

The algorithm is also subdivided into two parts. Part one (the game) scales with  $log_2P$  and uses 1 byte of memory. Part two scales as mentioned in chapter 2.2.1 with  $t_{bc}(P-1)$ . Thus the entire runtime can be estimated with  $(L+2 \cdot o) \cdot \lceil log_2P \rceil + t_{bc}(P-1)$ .

```

// parameters (given by environment)

set p = number of participating processors

set rank = my local id

// phase 1 - initialization (only once)

5

reserve flag with 1 entries as shared

set flag = 0

// phase 2 - done for every barrier

\textbf{set} \ \texttt{true} = 1

10

set false = 0

set round = -1

// repeat log(p) times

repeat

set round = round + 1

15

set peer = rank xor 2<sup>round</sup>

// I have no partner -> next round ....

if peer > p then

continue

20

ifend

// I am the winner

if rank > peer then

wait until flag == true

^{25}

set flag = false

else

set flag on peer = true

wait until flag == true

ifend

30

until round > Id(p)

// phase 3 - node 0 ever wins

if rank == 0 then

set flag in all other nodes to true

35

ifend

```

Listing 2.3: Pseudo Code for Tournament Barrier

#### 2.2.1.4 f-way Tournament

#### 2.2.1.4.1 Description

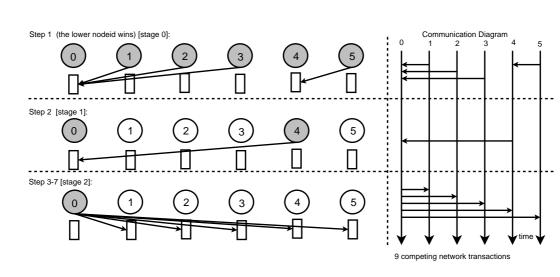

The f-way Tournament Barrier bases on the same principle as the Tournament Barrier (section 2.2.1.3). It was proposed by Grunwald et al. in 1993 [GV94]. The most important difference is that more than two processors are competing in one game. A graphical representation can be found in figure 2.7. The pseudo-code is nearly identical to the tournament barrier (see listing 2.3), only with more than two nodes.

#### 2.2.1.4.2 Conclusion

This barrier is suitable for special network topologies with a fan-out of more than one (e.g. torus networks). But should not scale better on standard central switching-based networks. The algorithm scales theoretically (with a fan-out of f in each node) with  $log_f P$  network transactions and 1 bytes of memory per node, but is practically limited by the network infrastructure which serializes and enqueues concurrent requests. Thus, the predicted runtime within our model is  $(L + f \cdot o) \cdot \lceil log_f P \rceil + t_{bc}(P-1)$ .

Figure 2.7: Example for the 4-way tournament algorithm between 6 nodes

## 2.2.1.5 MCS

#### 2.2.1.5.1 Description

The MCS Tree Barrier was proposed by Mellor-Crummey and Scott in 1991 [MCS91a, MCS91b, SMC94]. It uses also a tree structure and is quite similar to the Combining Tree barrier (see chapter 2.2.1.2). Each node is assigned to a tree node. The resulting n-ary tree consists of all nodes, each node has an array of n flags. All, but the top node write to their parent's node flag when all child nodes wrote the flag to them. All nodes, which have no children start with the array initialized with true. When the topmost node's flag array is completely filled, it notifies the others.

Figure 2.8: Example of the MCS Tree algorithm between 6 nodes

```

// parameters (given by environment)

set p = number of participating processors

set rank = my local id

set n = number of childnodes

\mathbf{5}

// phase 1 - initialization (only once)

set x = 0 // the barrier counter

reserve array with n+1 entries as shared

// -> array[n] acts as barrier_reached flag

10

// phase 2 - done for every barrier

set x = x + 1

// initialize my flags (flag = 1 if no child is present)

for j in 0...n–1 do

15

if p >= (rank * n) + 1 + j then

set array[j] = 0

else

set array[j] = 1

ifend

20

forend

set array[n] = 0

repeat

set parent = (rank-1) div n

25

set slot = (rank-1) \mod n

if sum(array[0..n-1]) == 4 then

if rank == 0 then

set array[n] = 1

30

else

set array[slot] in parent to 1

endif

endif

until array[n] == 1

35

// phase 3

if rank == 0 then

set array[n] in all other nodes to 1

ifend

40

```

Listing 2.4: Example of the MCS Tree algorithm between 6 nodes

## 2.2.1.5.2 Conclusion